ICSLV810

Description

The ICSLV810 is a low skew 1.5 V to 2.5 V, 1:10 fanout buffer. This device is specifically designed for data munications clock management. The large fanout from a single input line reduces loading on the input clock. The TTL level outputs reduce noise levels on the part. Typical applications are clock and signal distribution.

Features

- Packaged in 20-pin QSOP/SSOP

- Split 1:10 fanout Buffer

- Maximum skew between outputs of different

- -

- -

- -

- packages 0.75 ns Max propagation delay of 3.8 ns Operating voltage of 1.5 V to 2.5 V on Bank A Operating voltage of 1.5 V to 2.5 V on Banks B and C Advanced, low power, CMOS process Industrial temperature range -40° C to +85° C 3.3 V tolerant input when VDDA=2.5 V Available in Pb (lead) free packaging

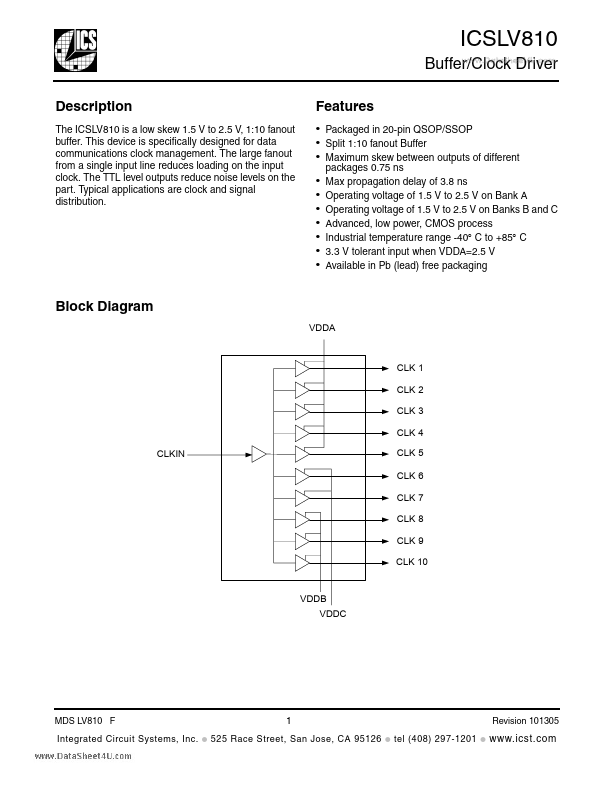

Block Diagram

VDDA

CLK 1 CLK 2 CLK 3 CLK 4 CLKIN CLK 5 CLK 6 CLK 7 CLK 8 CLK 9 CLK 10

VDDB VDDC

MDS LV810 F Integrated Circuit Systems, Inc.

- 1

525 Race Street, San Jose, CA 95126

- Revision 101305 tel (408) 297-1201

-...